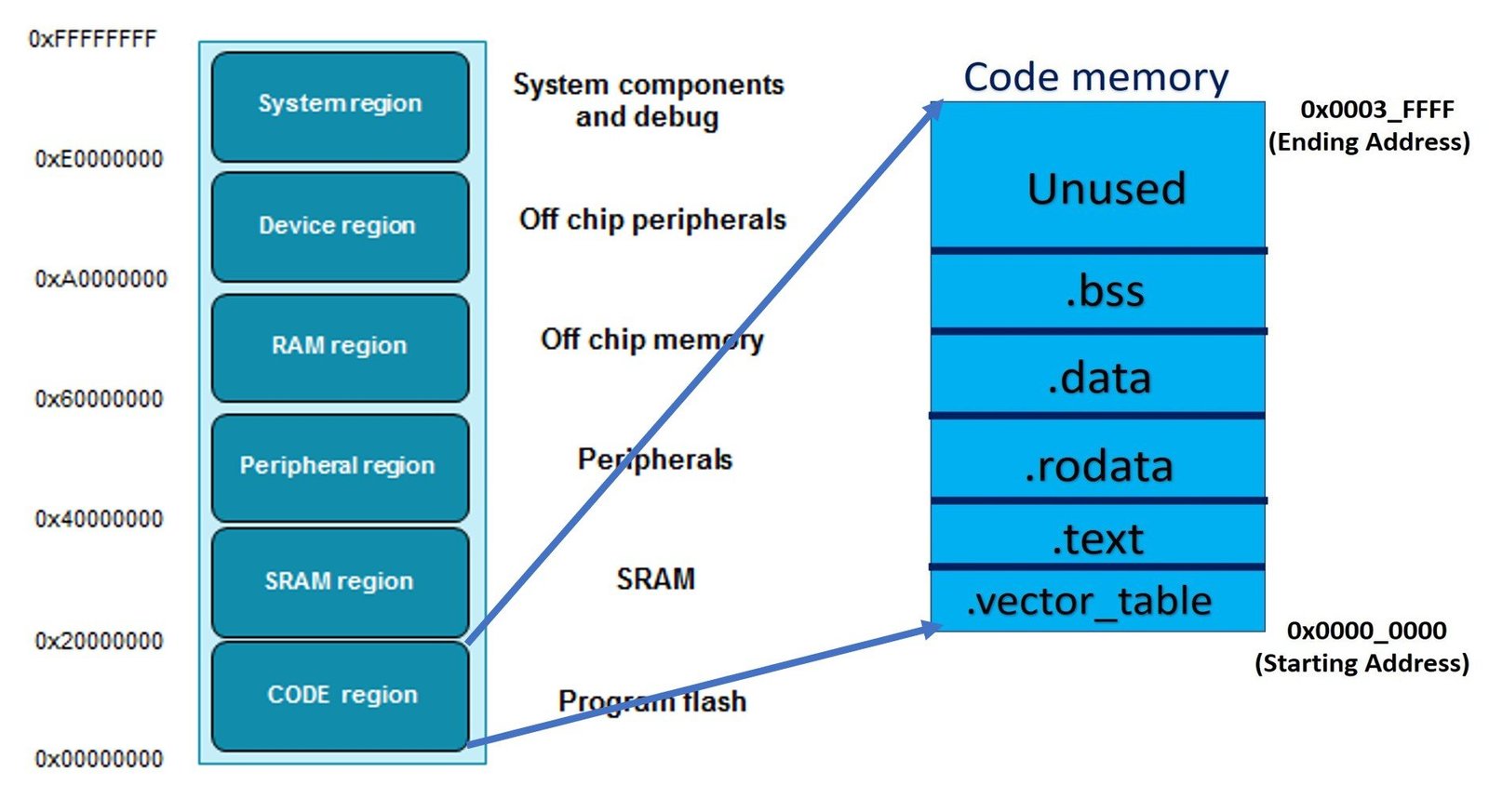

Cortex M Vector Table. 101093cercorbht358 PMC free article Google Scholar Malekmohammadi M AuYong N Price CM Tsolaki E Hudson AE Pouratian N 2018 Propofol-induced changes in α-β sensorimotor cortical connectivity. __INITIAL_SP __STACK_LIMIT __PROGRAM_START __VECTOR_TABLE __VECTOR_TABLE_ATTRIBUTE. This would explain why this bit has to be set accordingly telling the core to use the system bus and access the SRAM. I would like to have the option of relocating my vector table to RAM at runtime in a library ie if the code doesnt need to do this it doesnt and the RAM isnt allocated or is eliminated by section garbage collection during link The actual relcation seems simple enough but Im having trouble figuring out.

00xnor Sergey Ostrikov Cortex M4 Core Registers

00xnor Sergey Ostrikov Cortex M4 Core Registers From 00xnor.blogspot.com

00xnor Sergey Ostrikov Cortex M4 Core Registers

00xnor Sergey Ostrikov Cortex M4 Core Registers From 00xnor.blogspot.com

More related: Can I Buy A Suzuki Jimny In The Us - Geely Ge Car Price In India - Convert Jpg To Pdf Reduce Size - Cast Of From Russia With Love -

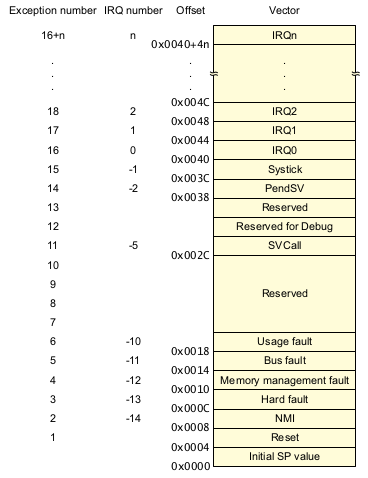

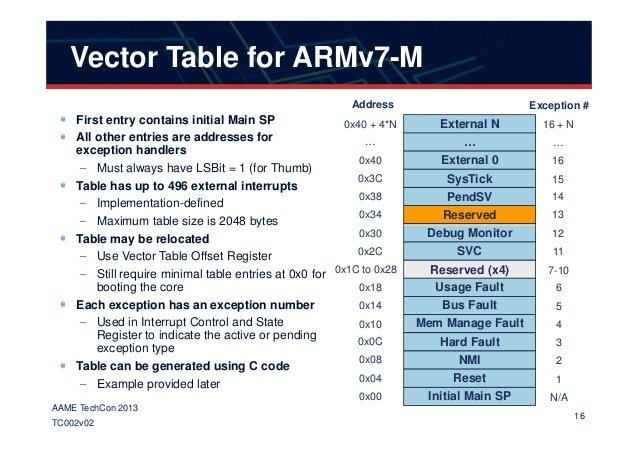

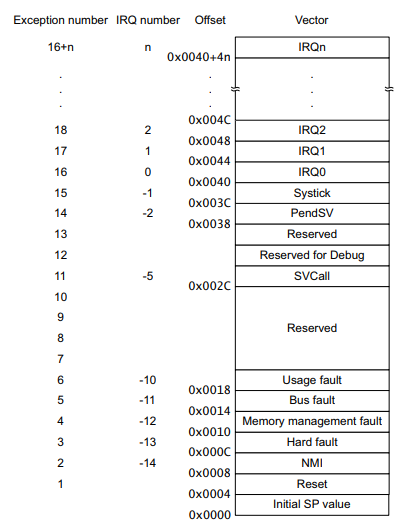

The Vector Table defines the entry addresses of the processor exceptions and the device specific interrupts. The ARM core up on boot up loads the stack pointer with the value stored at offset 0. Cereb Cortex 2516181628. As discussed earlier the ARM Cortex M series of MCUs typically carters to lower end application with the core running between a few MHz to a maximum 150MHz. According to the Cortex-M3 tech ref manual the VTOR is defined as. The Execution of the current task is suspended.

I would like to have the option of relocating my vector table to RAM at runtime in a library ie if the code doesnt need to do this it doesnt and the RAM isnt allocated or is eliminated by section garbage collection during link The actual relcation seems simple enough but Im having trouble figuring out.

The C startup file relys on certain compiler specific preprocessor defines specified in CMSIS compiler headers. Typically on power-on reset the Vector table base address is defined to be at 0. AREA Field in ARM Assembly. Cortex-m-rt separates the vector table in its own section named vector_table. How do I combine two hex files created by Keil uVision. 1 Cortex-M interrupt vector table alignment principle.

Interrupt Handling In Arm Cortex M Embien Technology Blog

Source: embien.com

Interrupt Handling In Arm Cortex M Embien Technology Blog

Source: embien.com

The vector table and interrupt service routinesexception handlers are defined inside the startup file of a microcontroller.

Arm Cortex M Interrupts And Freertos Part 1 Mcu On Eclipse

Source: mcuoneclipse.com

Arm Cortex M Interrupts And Freertos Part 1 Mcu On Eclipse

Source: mcuoneclipse.com

This is a 7-bit aligned address so its 7 LSBs must be zero which points to the location of this interrupt vector table.

Ruffian Heng Principle Of Embedded Cortex M Interrupt Vector Table And Its Redirection Method Develop Paper

Source: developpaper.com

Ruffian Heng Principle Of Embedded Cortex M Interrupt Vector Table And Its Redirection Method Develop Paper

Source: developpaper.com

To target low cost tools and ease of development the interrupt architecture is designed to be simpler and straight forward.

Interrupt Vector Table An Overview Sciencedirect Topics

Source: sciencedirect.com

Interrupt Vector Table An Overview Sciencedirect Topics

Source: sciencedirect.com

The Vector Table defines the entry addresses of the processor exceptions and the device specific interrupts.

Sequence Of Interrupt Processing Steps Arm Cortex M Microcontrollers

Source: microcontrollerslab.com

Sequence Of Interrupt Processing Steps Arm Cortex M Microcontrollers

Source: microcontrollerslab.com

Maybe on an interrupt the ICode bus is used which cannot access the SRAM even when remapped I dont know if this is true.

Cortex M0 Devices Generic User Guide

Source: developer.arm.com

The vector table and interrupt service routinesexception handlers are defined inside the startup file of a microcontroller.

Tock Embedded Operating System Walkthrough

Source: tockos.org

Tock Embedded Operating System Walkthrough

Source: tockos.org

Cortex-m-rt uses standard sections like text rodata bss and data as one would expect.

Interrupts

Source: download.mikroe.com

Interrupts

Source: download.mikroe.com

When an application is started by a bootloader in the same flash or even in RAM.

Cortex M0 Devices Generic User Guide

Source: developer.arm.com

The vector table in ARM Cortex M series looks like.

Cortex M0 Vector Table Avr Freaks

Source: avrfreaks.net

Cortex M0 Vector Table Avr Freaks

Source: avrfreaks.net

So we can see that the vectortable comes from the VTOR Vector Table Offset Register.

What Is Interrupt Vector Table In Arm Cortex M Microcontrollers

Source: microcontrollerslab.com

What Is Interrupt Vector Table In Arm Cortex M Microcontrollers

Source: microcontrollerslab.com

101093cercorbht358 PMC free article Google Scholar Malekmohammadi M AuYong N Price CM Tsolaki E Hudson AE Pouratian N 2018 Propofol-induced changes in α-β sensorimotor cortical connectivity.

Cortex M Geeks24 Eu

Source: geeks24.eu

Cortex M Geeks24 Eu

Source: geeks24.eu

According to the Cortex-M3 tech ref manual the VTOR is defined as.

What Is Interrupt Vector Table In Arm Cortex M Microcontrollers

Source: microcontrollerslab.com

What Is Interrupt Vector Table In Arm Cortex M Microcontrollers

Source: microcontrollerslab.com

According to the Cortex-M3 tech ref manual the VTOR is defined as.

Cortex M3 Devices Generic User Guide

Source: developer.arm.com

It is typically located at the beginning of the program memory however Using Interrupt Vector Remap it can be relocated to RAM.

00xnor Sergey Ostrikov Cortex M4 Core Registers

Source: 00xnor.blogspot.com

00xnor Sergey Ostrikov Cortex M4 Core Registers

Source: 00xnor.blogspot.com

Here is the full table for a Cortex M0.

Arm Cortex M Interrupts And Freertos Part 3 Mcu On Eclipse

Source: mcuoneclipse.com

Arm Cortex M Interrupts And Freertos Part 3 Mcu On Eclipse

Source: mcuoneclipse.com

Artisan Physical IP is available for free through the DesignStart Tier of Arm Flexible Access.

Arm Cortex M Interrupts And Freertos Part 1 Mcu On Eclipse

Source: mcuoneclipse.com

Arm Cortex M Interrupts And Freertos Part 1 Mcu On Eclipse

Source: mcuoneclipse.com

For MCU embedded with flash the initial interrupt vector table is generally required to be fixedly linked to the flash start address because the system startup always obtains the 0 initial stack and 1.

Exception Vector An Overview Sciencedirect Topics

Source: sciencedirect.com

Exception Vector An Overview Sciencedirect Topics

Source: sciencedirect.com

Cortex-M includes a vector table that contains the address of the interrupt service routines ISRs along with each interrupt number.